# S1D13515

## S1D13515 XGA External SDRAM Display Controller

The S1D13515 is a highly integrated LCD controller targeted at embedded markets. It advances on the successes of other Epson LCD controllers by embedding a proprietary 32-bit RISC CPU and associated accelerator blocks to achieve an increase in flexibility and functionality. Routines are provided allowing for audio playback, 2D BitBLT operations, warp and filtering operations, and the ability to offer OpenGL-ES 1.1 support. In particular, the Warp Logic functions make this an ideal solution for the automotive heads-up display (HUD) market, or pseudo 3D navigation displays.

The S1D13515 is an affordable, low power device which uses a flexible external SDRAM memory interface to provide its frame buffer. It supports a wide variety of CPU interfaces and LCD panel outputs which makes it an excellent choice for instrumentation or center cluster applications.

NOTE: S2D13515 is also available and meets automotive specifications.

#### **FEATURES**

- Direct and indirect CPU interfaces

- SPI or I2C host interface

- Memory interface for x16 or x32 external SDRAM (x32 available on S1D13513 PBGA only)

- Can display 2 RGB panels simultaneously (some restrictions apply)

- Support for single RGB panel with serial command interface

- Programmable resolutions and color depths up to 32 bpp

- Video input / camera port supporting flexible configurations of 8-bit cameras and RGB input streams

- Sprite engine with up to 8 sprites

- Multiple windows supporting alpha blending, double buffering, and horizontal flip

- 32-bit embedded RISC processor with accelerator blocks

- o Audio playback (WAV, Ogg Vorbis, etc.)

- OpenGL-ES 1.1 compliant

- 2D BitBLT Acceleration with API

- Programmable startup sequence without host

- 2 channel PWM

- I2S and I2C outputs

- SPI flash memory interface

- Keypad interface (5x5 matrix support)

- Temperature range:

- -40 to +85 °C

- Package: QFP22-256 and PBGA1U-256

- Warp logic for HUD projection correction or other distortion compensation

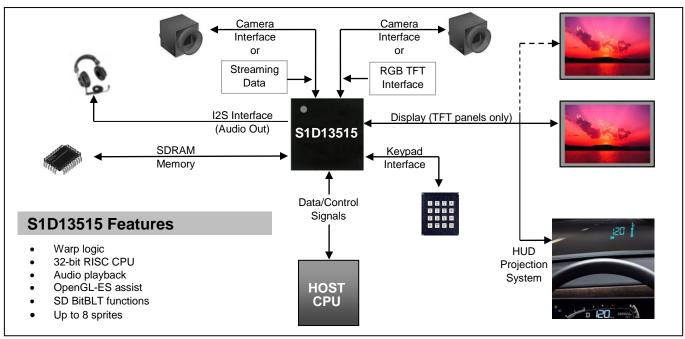

#### SYSTEM BLOCK DIAGRAM

### DESCRIPTION

#### **External Display Buffer**

- Uses external SDRAM as display buffer

- Supports x32 SDRAM interface (Size: 16/32/64M byte)

- SDRAM clock: 100MHz

- External memory is accessible by the internal and host CPUs

- Provides configurable linear access to memory in 4 MB paging windows

#### **CPU Interface**

- Direct and indirect as well as serial host interface support for most popular CPU interfaces

- SPI or I2C host interface

- Supports 25MHz host bus clock

#### **Display Support**

- Single or dual panel implementations (dual can have independent images)

- Color TFT panel with optional serial command interface

- Color depths: 8/16/24 bpp

- Target resolutions / color depths

- o 1024x768@24 bpp, 60Hz

- 800x480 & 320x240 simultaneous @24 bpp, 60Hz

#### **Display Features**

- Warp logic corrects projection anomalies on HUD

- Multiple windows layers support:

- Horizontal flip

- Double buffering

- o Alpha blending

- Sprite engine supports up to 8 sprite layers with alpha blending and transparency

- Interrupts available

- Maskable non-display (Vsync) interrupt

- Delayed version of Vsync Interrupt

#### **Embedded CPU**

- Embedded CPU Speed: 50MHz (typical)

- 32-bit RISC CPU can be used for : • Audio decode (supported codecs: MP3, AAC, WAV,

- ADPCM, Ogg Vorbis)

- 2D BitBLT acceleration with API

- OpenGL-ES assist (OpenGL-ES v1.1 compliant)

- OEM defined functions

#### **Digital Video**

- Video input / camera port supporting either 1x 8-bit camera, 2x 8-bit cameras, 1x RGB data stream, 2x RGB data streams, simultaneous 1x 8-bit and 1x RGB data stream input (when second camera input is used only single panel is available). Supports resize function of the video in stream

- Supports ITU-R BT.656 YUV format

- Supports down-scaling of the video input stream

- Captures YUV data into SDRAM as RGB format

#### Miscellaneous

- Internal system speed: 50MHz typical

- 2 channel PWM for backlight control

- I2C interface (typically used for camera)

- I2S interface (typically used for audio output)

- SPI flash memory interface

- Keypad interface with 5 x 5 matrix support

- General purpose input/output pins available

- Flexible clock structure with two embedded PLLs:

- Two embedded PLLS

- o Built-in crystal input

- Digital clock input

- Clocks dynamically turned off for power saving

- Operating temperature: -40 to +85°C

- COREVDD 1.8 volts and IOVDD 3.3 volts

- Package: QFP22-256 and PBGA1U-256

For more information on the S1D13515 and other Epson Display Controllers, visit the Epson Global website.

https://global.epson.com/products and drivers/semicon/products/display controllers/

For Sales and Technical Support, contact the Epson representative for your region.

https://global.epson.com/products\_and\_drivers/semicon/information/support.html

Document code: X83A-C-001-02.2

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies. ©Seiko Epson Corporation 2007 - 2018. All rights reserved.